- 您现在的位置:买卖IC网 > Sheet目录2009 > MAX19711ETN+T (Maxim Integrated Products)IC ANLG FRNT END 56-TQFN

MAX19711

10-Bit, 11Msps, Full-Duplex

Analog Front-End

______________________________________________________________________________________

29

Applications Information

Using Balun Transformer AC-Coupling

An RF transformer (Figure 10) provides an excellent

solution to convert a single-ended signal source to a

fully differential signal for optimum ADC performance.

Connecting the center tap of the transformer to COM

provides a VDD / 2 DC level shift to the input. A 1:1

transformer can be used, or a step-up transformer can

be selected to reduce the drive requirements. In gener-

al, the MAX19711 provides better SFDR and THD with

fully differential input signals than single-ended signals,

especially for high input frequencies. In differential

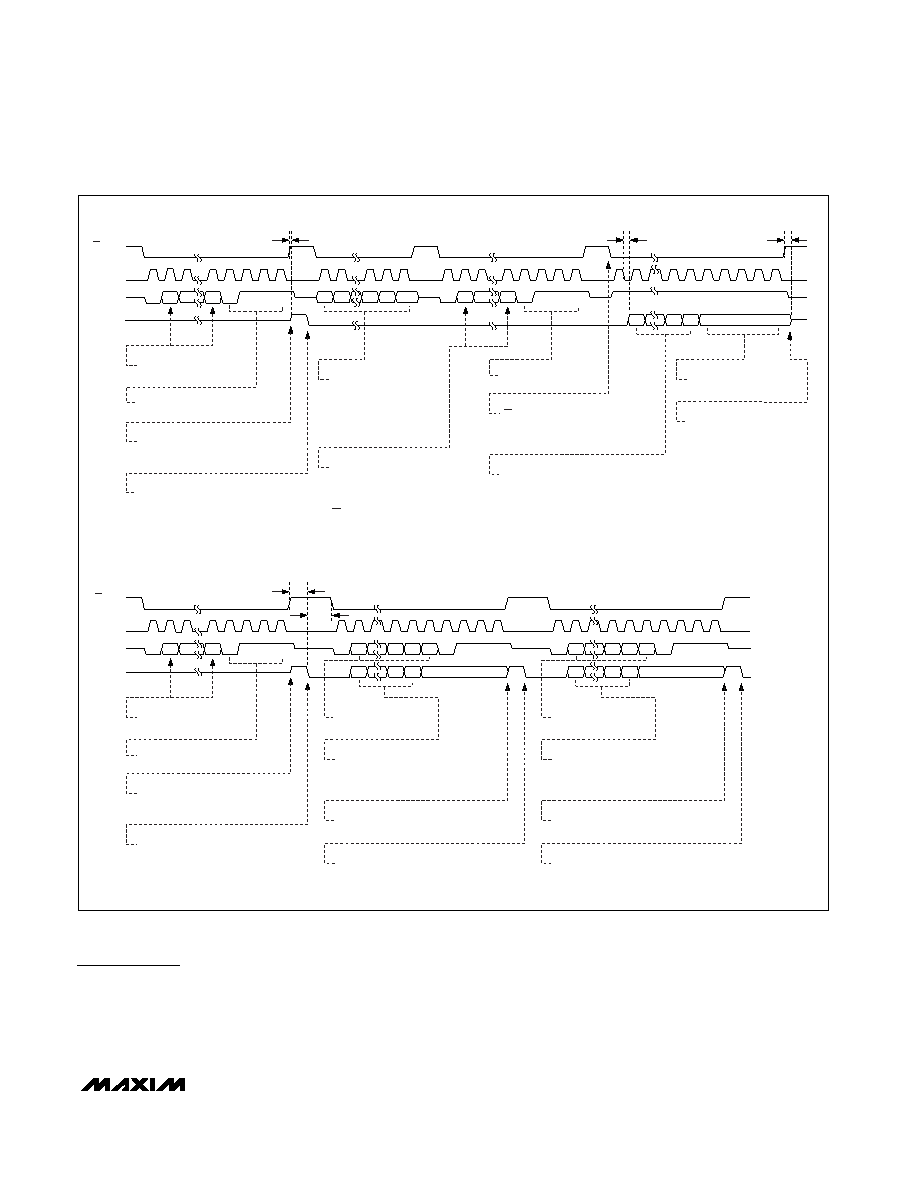

Figure 9. Aux-ADC Conversions Timing

CS/WAKE

2. CONTINUOUS AUX-ADC CONVERSIONS

tDCS

tCONV

SCLK

00

01

1

11

1

00

1

11

1

00

1

11

16

1

10

11

12

13

14

15

16

1

10

11

12

13

14

15

16

1

DIN

DOUT

D1

D0

D0 HELD

D9

D1

D0

D0 HELD

D9

FIRST 10 BIT AUX-ADC

CONVERSION RESULT IS

SHIFTED OUT ON DOUT ON

THE FALLING EDGE OF SCLK

MSB FIRST

SECOND 10 BIT AUX-ADC

CONVERSION RESULT IS

SHIFTED OUT ON DOUT ON

THE FALLING EDGE OF SCLK

MSB FIRST

AD10 = 1, AD0 = 1,

PERFORM CONVERSION,

DOUT ENABLED

AD10 = 1, AD0 = 1,

PERFORM CONVERSION,

DOUT ENABLED

AD10 = 1, AD0 = 1,

PERFORM CONVERSION,

DOUT ENABLED

DOUT TRANSITIONS FROM

HIGH IMPEDANCE TO LOGIC-

HIGH INDICATING START OF

FIRST CONVERSION

DOUT TRANSITIONS HIGH

INDICATING START OF

SECOND CONVERSION

DOUT TRANSITIONS HIGH

INDICATING START OF

THIRD CONVERSION

DOUT TRANSITIONS LOW

INDICATING END OF FIRST

CONVERSION, DATA IS AVAILABLE

AND CAN BE SHIFTED OUT IF DOUT

IS ENABLED, AD0 CLEARED

DOUT TRANSITIONS LOW

INDICATING END OF SECOND

CONVERSION, DATA IS AVAILABLE

AND CAN BE SHIFTED OUT IF DOUT

IS ENABLED, AD0 CLEARED

DOUT TRANSITIONS LOW

INDICATING END OF THIRD

CONVERSION, DATA IS AVAILABLE

AND CAN BE SHIFTED OUT IF DOUT

IS ENABLED, AD0 CLEARED

AUX-ADC REGISTER

ADDRESS

tCSD

tCD

tCHZ

CS/WAKE

SCLK

1. SINGLE AUX-ADC CONVERSION WITH CONVERSION DATA READOUT AT A LATER TIME

1

00

1

0

1

0

1

DIN SET HIGH DURING SINGLE READ

11

16

1

16

1

16

1

16

10

D1

D0

D0 HELD

D9

11

DIN

DOUT

AD10 = 0, AD0 = 1,

PERFORM CONVERSION,

DOUT DISABLED

DOUT TRANSITIONS FROM

HIGH IMPEDANCE TO LOGIC-

HIGH INDICATING START OF

CONVERSION

DOUT TRANSITIONS LOW

INDICATING END OF CONVERSION,

DATA IS AVAILABLE AND CAN BE

SHIFTED OUT IF DOUT IS ENABLED,

AD0 CLEARED

0

IF AUX-ADC CONVERSION

DOES NOT NEED TO BE

READ IMMEDIATELY, THE SPI

INTERFACE IS FREE AND

CAN BE USED FOR OTHER

FUNCTIONS, SUCH AS

HOUSEKEEPING AUX-DAC

ADJUSTMENT, ETC.

AUX-ADC REGISTER

ADDRESS

CONVERSION RESULT DATA

BIT D0 IS HELD FOR THE SIX

LEAST SIGNIFICANT BITS

DOUT TRANSITIONS TO

HIGH-IMPEDANCE

10 BIT AUX-ADC

CONVERSION RESULT IS

SHIFTED OUT ON DOUT ON

THE FALLING EDGE OF SCLK

MSB FIRST

AUX-ADC REGISTER

ADDRESS

AD10 = 1, AD0 = 0,

AUX-ADC IDLE

(NO CONVERSION),

DOUT ENABLED AND

CONVERSION DATA IS

SHIFTED OUT ON NEXT

CS/WAKE FALLING EDGE

FIRST FALLING EDGE OF

CS/WAKE AFTER DOUT IS

ENABLED STARTS SHIFTING THE

AUX-ADC CONVERSION DATA ON

THE FALLING EDGE OF SCLK

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX19712ETN+T

IC ANLG FRNT END 56-TQFN

MAX19713ETN+T

IC ANLG FRNT END 56-TQFN

MAX271ENG+

IC FILTER LOWPASS PROG 24-DIP

MAX274ACWI+T

IC FILTER ANALOG 8TH-ORD 28SOIC

MAX281AEWE+

IC FILTER 5TH-ORD BESSEL 16-SOIC

MAX294CSA+

IC FILTER LOWPASS 8TH 8-SOIC

MAX295ESA+

IC FILTER LOWPASS 8-SOIC

MAX3634ETM+T

IC CLOCK PHASE ALIGNER 48-TQFN

相关代理商/技术参数

MAX19711ETN-T

功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40

MAX19711EVCMODU+

功能描述:数据转换 IC 开发工具 MAX19710/13 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX19711EVKIT

功能描述:数据转换 IC 开发工具 RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX19711EVKIT+

功能描述:数据转换 IC 开发工具 MAX19710/13 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX19712ETN

功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40

MAX19712ETN+

功能描述:ADC / DAC多通道 22Msps CODEC/AFE Full Duplex RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40

MAX19712ETN+T

功能描述:ADC / DAC多通道 22Msps CODEC/AFE Full Duplex RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40

MAX19712ETN-T

功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40